## May/June 2012. P31/32

5 The table shows the assembly language instructions for a processor which has one general purpose register – the Accumulator.

| Instruction |                     |                                                            |  |

|-------------|---------------------|------------------------------------------------------------|--|

| Op Code     | Operand             | Explanation                                                |  |

| LDD         | <address></address> | Load using direct addressing                               |  |

| STO         | <address></address> | Store the contents of the Accumulator at the given address |  |

| LDI         | <address></address> | Load using indirect addressing                             |  |

| LDX         | <address></address> | Load using indexed addressing                              |  |

| INC         |                     | Add 1 to the contents of the Accumulator                   |  |

| END         |                     | End the program and return to the operating system         |  |

| 500 | LDD | 507 |  |

|-----|-----|-----|--|

| 501 | INC |     |  |

| 502 | STO | 509 |  |

| 503 | LDD | 508 |  |

| 504 | INC |     |  |

| 505 | STO | 510 |  |

| 506 | END |     |  |

| 507 | 22  |     |  |

| 508 | 170 |     |  |

| 509 | 0   |     |  |

| 510 | 0   |     |  |

|     |     |     |  |

|             |     | Memory | Address<br>509 |     |

|-------------|-----|--------|----------------|-----|

| Accumulator | 507 | 508    | 509            | 510 |

|             | 22  | 170    | 0              | 0   |

|             |     |        |                |     |

|             |     |        |                |     |

|             |     |        |                |     |

|             |     |        |                |     |

|             |     |        |                |     |

|             |     |        |                |     |

## May/June 2012. P33

6 The table shows the assembly language instructions for a processor which has one general purpose register – the Accumulator.

| Instruction |                     |                                                            |  |

|-------------|---------------------|------------------------------------------------------------|--|

| Op Code     | Operand             | Explanation                                                |  |

| LDD         | <address></address> | Load using direct addressing                               |  |

| STO         | <address></address> | Store the contents of the Accumulator at the given address |  |

| LDI         | <address></address> | Load using indirect addressing                             |  |

| LDX         | <address></address> | Load using indexed addressing                              |  |

| INC         |                     | Add 1 to the contents of the Accumulator                   |  |

| END         |                     | End the program and return to the operating system         |  |

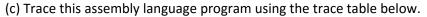

(c) Trace this assembly language program using the given trace table. The first instruction of the program is loaded into main memory at address 200.

| 200 | LDD | 208 |  |

|-----|-----|-----|--|

| 201 | INC |     |  |

| 202 | STO | 208 |  |

| 203 | LDD | 207 |  |

| 204 | INC |     |  |

| 205 | STO | 207 |  |

| 206 | END |     |  |

| 207 | 16  |     |  |

| 208 | 150 |     |  |

|     |     |     |  |

|             | Memory Address |     |  |

|-------------|----------------|-----|--|

| Accumulator | 207            | 208 |  |

|             | 16             | 150 |  |

|             |                |     |  |

|             |                |     |  |

|             |                |     |  |

|             |                |     |  |

|             |                |     |  |

[4]

#### May/June 2013. P31/32

3 The table shows the assembly language instructions for a processor which has one general purpose register – the Accumulator (ACC), and an index register (IX).

| Instruction |                       | Evaluation                                                                                                                 |  |  |

|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Op Code     | Operand               | - Explanation                                                                                                              |  |  |

| LDD         | <address></address>   | Direct addressing. Load the contents of the given address to ACC                                                           |  |  |

| STO         | <address></address>   | Store the contents of ACC at the given address                                                                             |  |  |

| LDI         | <address></address>   | Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC       |  |  |

| LDX         | <address></address>   | Indexed addressing. Form the address as <address> + the contents of IX. Copy the contents of this address to ACC</address> |  |  |

| INC         | <register></register> | Add 1 to the contents of the register (ACC or IX)                                                                          |  |  |

| ADD         | <address></address>   | Add the contents of the given address to the contents of ACC                                                               |  |  |

| OUT         |                       | Output the contents of ACC (as a denary number) to the monitor                                                             |  |  |

| IN          |                       | Input a denary number from the keyboard and store in ACC                                                                   |  |  |

| END         |                       | End the program and return to the operating system                                                                         |  |  |

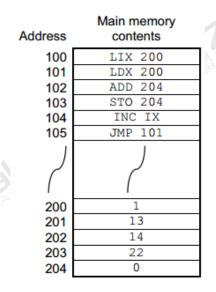

The diagram shows a program loaded in main memory starting at location 100.

Two of the op-codes have been partially blanked out.

Locations 200 onwards contain data which is used by the program.

(c) The instruction at address 105 is fetched and executed.

Draw on the diagram to explain how this instruction is executed and show the contents of ACC after execution.

**Topical Past Papers**

# Topic: 1.4.4 Assembly Language

[2]

### May/June 2013. P31/32

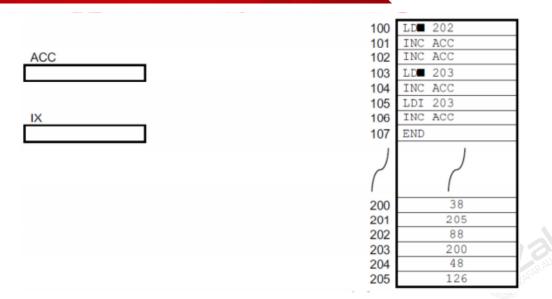

6 A multiprogramming, multi-user operating system organises the available memory into two fixed sized partitions.

- Partition 1 size 30 Gb is used only for batch processing

- Partition 2 size 40 Gb is used only for interactive processing at a terminal

[1]

[1]

## Topic: 1.4.4 Assembly Language

(i) If PROG6 completes execution, which programs (if any) can be loaded next?

(ii) If PROG8 completes execution, which programs (if any) can be loaded next?

### Oct/Nov 2013. P31

3 (c) The diagram shows a program loaded into main memory starting at memory address 7A Hex.

Address Hex.) 7A 2150 7B A351 7C A552 7D FFFF 90 003C

(i) How many bits are used for each main memory location?

[1]

The trace table below is used to show how the contents of the special-purpose registers change as the program is executed. The steps in the fetch stage of the fetch-execute cycle are shown in the first column using register transfer notation. (For example, MAR  $\leftarrow$  [PC] means the content of the Program Counter is copied to the Memory Address Register.)

## (ii) Complete the trace table for the fetching of the **first program instruction (2150)**:

- Show the changing contents of the registers

- Put a tick in the Address bus/Data bus column to show when the signals on that bus change.

| 13   | Fetch<br>stage | Special purpose registers<br>(Contents shown in Hex.) |     |     |     | Buses       |          |

|------|----------------|-------------------------------------------------------|-----|-----|-----|-------------|----------|

| LASP |                | PC                                                    | MAR | MDR | CIR | Address bus | Data bus |

|      |                | 7A                                                    |     |     |     |             |          |

|      | MAR ← [PC]     |                                                       |     |     |     |             |          |

|      | PC ← [PC] + 1  |                                                       |     |     |     |             |          |

|      | MDR ← [[MAR]]  |                                                       |     |     |     |             |          |

|      | CIR ← [MDR]    |                                                       |     |     |     |             |          |

(d) The following table shows some of a processor's instruction set in assembly language.

| Instruction |                     | Exploration                                                                                                                |  |

|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Op Code     | Operand             | Explanation                                                                                                                |  |

| LDD         | <address></address> | Direct addressing. Load the contents of the given address to ACC                                                           |  |

| LDI         | <address></address> | Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC       |  |

| LIX         | <address></address> | Load the contents of the address to the Index register (IX)                                                                |  |

| LDX         | <address></address> | Indexed addressing. Form the address as <address> + the contents of IX. Copy the contents of this address to ACC</address> |  |

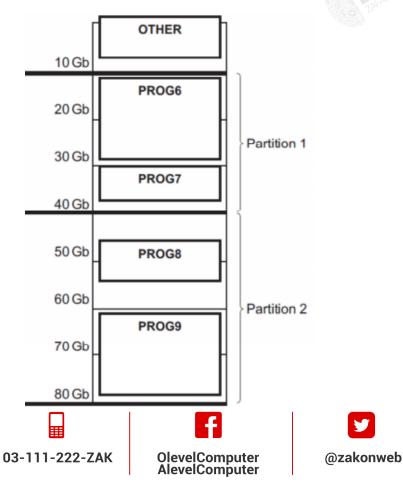

The following program is to be executed. Shown are:

- the first four instructions only of this program

- the memory locations which are accessed by this program.

Complete the trace table below for the first four program instructions. Show each change in the contents of the

|             | Register          |                     |  |  |

|-------------|-------------------|---------------------|--|--|

| Instruction | Accumulator (ACC) | Index Register (IX) |  |  |

| LIX 200     |                   |                     |  |  |

| LDD 201     |                   |                     |  |  |

| LDI 201     |                   |                     |  |  |

| LDX 201     |                   |                     |  |  |

### Oct/Nov 2013. P32

registers.

3 (c) The diagram shows a program loaded into main memory starting at memory address 30 Hex.

| ddress | Main memory<br>(contents shown in<br>Hex.) |

|--------|--------------------------------------------|

| 30     | 2150                                       |

| 31     | A351                                       |

| 32     | A552                                       |

| 33     | FFFF                                       |

| لم     | لم                                         |

| 58     | 003C                                       |

| 59     | 103C                                       |

| 5A     | 010B                                       |

(i) How many bytes are used to store each program instruction?

A

(ii) Describe the steps in the fetch stage of the fetch-execute cycle. Refer to the instruction at address 30 to illustrate your answer.

[1]

zak@zakonweb.com

Page **7** of **16**

www.zakonweb.com

[4]

| (d) The following table shows some of a processor's instruction set in assembly lan | guage. |

|-------------------------------------------------------------------------------------|--------|

|-------------------------------------------------------------------------------------|--------|

| Instr   | ruction               | Explanation                                                                                                                |

|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| Op Code | Operand               | Explanation                                                                                                                |

| LIX     | <address></address>   | Load the contents of the address to the Index register (IX)                                                                |

| LDX     | <address></address>   | Indexed addressing. Form the address as <address> + the contents of IX. Copy the contents of this address to ACC</address> |

| STO     | <address></address>   | Store the contents of ACC at the given address                                                                             |

| ADD     | <address></address>   | Add the contents of the given address to the ACC                                                                           |

| INC     | <register></register> | Add 1 to the contents of the register (ACC or IX)                                                                          |

| JMP     | <address></address>   | Jump to the given address                                                                                                  |

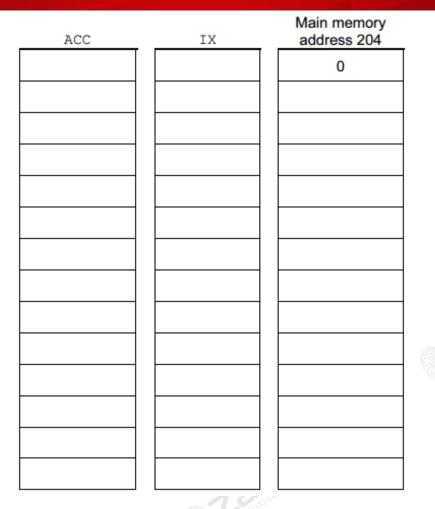

The following program is to be executed. Shown are:

- the first six instructions of this program

- the memory locations which will be accessed by this program.

Complete the trace table below for **three** iterations of the loop. Show each change to the contents of the registers and memory location 204.

zak@zakonweb.com

# **Computer Science 9608**

**Topical Past Papers**

## Topic: 1.4.4 Assembly Language

[4]

### Oct/Nov 2013. P33

(c) The diagram shows a program loaded into main memory starting at memory address 40 Hex.

| Address | Main memory<br>(Contents shown in<br>Hex.) |

|---------|--------------------------------------------|

| 40      | 7324                                       |

| 41      | A351                                       |

| 42      | A552                                       |

| 43      | FFFF                                       |

| لم      | لم                                         |

| 68      | 003C                                       |

| 69      | 103C                                       |

| 6A      | 010B                                       |

zak@zakonweb.com

[1]

# Topic: 1.4.4 Assembly Language

(i) How many bytes are used to store each program instruction?

(ii) Describe the steps in the fetch stage of the fetch-execute cycle. Use the instruction at address 40 to illustrate your answer. [5]

(d) The following table shows some of a processor's instruction set in assembly language.

| Inst    | ruction               | Evaluation                                                                                                           |  |

|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Op Code | Operand               | Explanation                                                                                                          |  |

| LDD     | <address></address>   | Direct addressing. Load the contents of the given address to ACC                                                     |  |

| LDI     | <address></address>   | Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC |  |

| STO     | <address></address>   | Store the contents of ACC at the given address                                                                       |  |

| ADD     | <address></address>   | Add the contents of the given address to the ACC                                                                     |  |

| INC     | <register></register> | Add 1 to the contents of the register (ACC or IX)                                                                    |  |

| JMP     | <address></address>   | Jump to the given address                                                                                            |  |

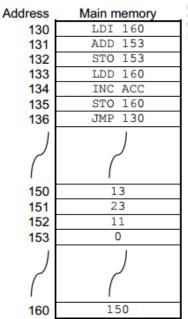

The following program is to be executed. Shown are:

- the first seven instructions in this program

- the memory locations which will be accessed by this program

www.zakonweb.com

Complete the trace table below for **two** iterations of the loop. Show each change in the contents of the register and memory locations.

| Register<br>ACC | Memory | / location |

|-----------------|--------|------------|

| ACC             | 153    | 160        |

|                 | 0      | 150        |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

|                 |        |            |

[4]

zak@zakonweb.com

www.zakonweb.com

Oct/Nov 2014. P31

### Oct/Nov 2014. P33

4 The table below gives a subset of the assembly language instructions for a computer with a single general-purpose register, the Accumulator (ACC), and an index register (IX).

| Instr                | uction                |                    |                                                                                                                                    |

|----------------------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Opcode<br>(mnemonic) | Operand               | Opcode<br>(binary) | Explanation                                                                                                                        |

| LDD                  | <address></address>   | 0000 0100          | Direct addressing. Load the contents of the given<br>address to ACC                                                                |

| LDV                  | <number></number>     | 0000 0101          | Load the given number to ACC                                                                                                       |

| STO                  | <address></address>   | 0001 0000          | Store the contents of ACC at the given address                                                                                     |

| LDI                  | <address></address>   | 0000 0110          | Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC               |

| LDX                  | <address></address>   | 0000 0111          | Indexed addressing. Form the address as <address><br/>+ the contents of IX. Copy the contents of this address<br/>to ACC</address> |

| INC                  | <register></register> | 0000 0011          | Add 1 to the contents of the register (ACC or IX)                                                                                  |

| OUTCH                |                       | 1000 0001          | Output to the monitor the character corresponding to the ASCII character code in ACC                                               |

| IN                   |                       | 1001 0000          | Input a denary number from the keyboard and store in ACC                                                                           |

| JMP                  | <address></address>   | 1100 1000          | Unconditional jump to the given address                                                                                            |

| END                  |                       | 1111 1111          | End the program and return to the operating system                                                                                 |

The diagram shows a program loaded in main memory starting at location 100. Locations 200 onwards contain data which are used by the program.

# Computer Science 9608 Topical Past Papers

[3]

## Topic: 1.4.4 Assembly Language

(b)

(a) (i) The instruction at address 102 is fetched.

| ACC                                                              | 100                       | LDI      | 150                        |

|------------------------------------------------------------------|---------------------------|----------|----------------------------|

|                                                                  | 101                       | OUTCH    | ł                          |

|                                                                  | 102                       | LDD      | 203                        |

|                                                                  | 103                       | INC      | ACC                        |

|                                                                  | 104                       | STO      | 150                        |

| IX                                                               | 105                       | JP       | 100                        |

|                                                                  | 106                       | END      |                            |

|                                                                  | 107                       |          |                            |

|                                                                  |                           |          | ) ]                        |

| Show the contents of the registers after execution.              |                           | 1        | $\boldsymbol{\mathcal{C}}$ |

|                                                                  | 150                       |          | 200                        |

| Write on the diagram to explain.                                 | [2]                       |          | ) )                        |

|                                                                  |                           |          | $\boldsymbol{\mathcal{C}}$ |

| <ol><li>ii) The instruction at address 100 is fetched.</li></ol> | 200                       |          | 65                         |

| ACC                                                              | 201                       |          | 76                         |

| 700                                                              | 202                       |          | 65                         |

|                                                                  | 203                       |          | 77                         |

|                                                                  | 204                       |          | 32                         |

|                                                                  | 205                       |          | 32                         |

| N                                                                | They are                  |          |                            |

| IX UNR                                                           |                           |          |                            |

|                                                                  |                           |          |                            |

|                                                                  |                           |          |                            |

|                                                                  |                           |          |                            |

| Show the contents of the registers after execution. We           | rite on the diagram to ex | plain.   |                            |

| The given table of instructions shows the binary numb            | er used for each instruct | ion's or | ocode.                     |

| All instructions in machine code are stored as a 16-bit          |                           |          |                            |

|                                                                  | pattern, when the optout  |          |                            |

| operand as the second 8 bits.                                    |                           |          |                            |

| (ii)  | Con  | sider   | the i | nstru  | ction: |        |       |        |         |        |        |       |        |         |        |      |         |     |

|-------|------|---------|-------|--------|--------|--------|-------|--------|---------|--------|--------|-------|--------|---------|--------|------|---------|-----|

|       | 0    | 0       | 0     | 1      | 0      | 0      | 0     | 0      | 0       | 1      | 0      | 0     | 0      | 0       | 0      |      | 1       |     |

|       | Des  | cribe   | what  | this i | instru | iction | does  | 5.     |         |        |        |       |        |         |        |      |         | [2] |

| (iii) | Prog | grami   | mers  | prefe  | r to v | vrite  | mach  | ine c  | ode ir  | nstruc | ctions | in he | exade  | cimal   | l. Exp | olai | in why. | [1] |

| (iv)  | Wha  | at is t | he he | exade  | cimal  | num    | ber f | or the | e insti | ructio | n sho  | wn ir | n part | : (b)(i | i)?    |      |         | [1] |

[2]

## Topic: 1.4.4 Assembly Language

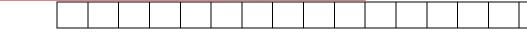

| (vi) | LDV 15 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|------|--------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|      |        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

(c) Use the ASCII code table to trace the **first four iterations** of the given program.

|                 | ASCII code table (part) |           |         |           |         |  |  |

|-----------------|-------------------------|-----------|---------|-----------|---------|--|--|

| Character       | Decimal                 | Character | Decimal | Character | Decimal |  |  |

| <space></space> | 32                      | I.        | 73      | R         | 82      |  |  |

| А               | 65                      | J         | 74      | S         | 83      |  |  |

| В               | 66                      | к         | 75      | т         | 84      |  |  |

| С               | 67                      | L         | 76      | U         | 85      |  |  |

| D               | 68                      | М         | 77      | V         | 86      |  |  |

| E               | 69                      | N         | 78      | w         | 87      |  |  |

| F               | 70                      | 0         | 79      | х         | 88      |  |  |

| G               | 71                      | Р         | 80      | Y         | 89      |  |  |

| н               | 72                      | Q         | 81      | Z         | 90      |  |  |

|      | ACC        | Location<br>150          | OUTPUT       | r          |

|------|------------|--------------------------|--------------|------------|

|      |            |                          |              |            |

|      |            |                          |              | 100        |

|      |            |                          |              | 101        |

|      |            |                          |              | 102<br>103 |

|      |            |                          |              | 104        |

|      |            |                          |              | 105        |

|      |            |                          |              | 106<br>107 |

|      |            |                          |              |            |

|      |            |                          |              |            |

|      |            |                          |              | 150        |

|      |            |                          |              |            |

|      |            |                          |              | 200        |

|      |            |                          |              | 201        |

|      |            |                          |              | 202        |

|      |            |                          |              | 204        |

|      |            |                          |              | 205        |

|      |            |                          | I            |            |

|      |            |                          | _            |            |

| 03-1 | 11-222-ZAK | OlevelComp<br>AlevelComp | uter<br>uter | @zakonweb  |

| 100 | LDI  | 150                         |  |

|-----|------|-----------------------------|--|

| 101 | OUTC | Н                           |  |

| 102 | LDD  | 150                         |  |

| 103 | INC  | ACC                         |  |

| 104 | STO  | 150                         |  |

| 105 | JP   | 100                         |  |

| 106 | END  |                             |  |

| 107 |      |                             |  |

| 150 |      | <u>ر کر</u><br>200<br>کر کر |  |

| 200 |      | 65                          |  |

| 201 |      | 76                          |  |

| 202 |      | 65                          |  |

| 203 |      | 77                          |  |

| 204 |      | 32                          |  |

| 205 |      | 32                          |  |

|     |      |                             |  |

zak@zakonweb.com

www.zakonweb.com

Page 14 of 16

### Oct/Nov 2014. P32

4 The table below gives a subset of the assembly language instructions for a computer with a single general purpose register, the Accumulator (ACC), and an index register (IX).

| Instru               | uction                |                    |                                                                                                                                   |

|----------------------|-----------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Opcode<br>(mnemonic) | Operand               | Opcode<br>(binary) | Explanation                                                                                                                       |

| LDD                  | <address></address>   | 0000 0100          | Direct addressing. Load the contents of the given address to ACC                                                                  |

| LDV                  | <number></number>     | 0000 0101          | Load the given number to ACC                                                                                                      |

| STO                  | <address></address>   | 0001 0000          | Store the contents of ACC at the given address                                                                                    |

| LDI                  | <address></address>   | 0000 0110          | Indirect addressing. At the given address is the<br>address to be used. Load the contents of this<br>second address to ACC        |

| LDX                  | <address></address>   | 0000 0111          | Indexed addressing. Form the address as<br><address> + the contents of IX. Copy the contents<br/>of this address to ACC</address> |

| INC                  | <register></register> | 0000 0011          | Add 1 to the contents of the register (ACC or IX)                                                                                 |

| OUTCH                |                       | 1000 0001          | Output the character corresponding to the ASCII character code in ACC to the monitor                                              |

| IN                   |                       | 1001 0000          | Input a denary number from the keyboard and store in ACC                                                                          |

| JMP                  | <address></address>   | 1100 1000          | Unconditional jump to the given address                                                                                           |

| CMP                  | <number></number>     | 1100 1001          | Compare the contents of ACC with the given number                                                                                 |

| JPE                  | <address></address>   | 1110 0111          | If the result of the previous compare instruction was a match, jump to the given address                                          |

(a) The given table of instructions shows the binary number used for each instruction's opcode. All instructions in machine code are stored as a 16-bit pattern, with the opcode as the first 8 bits and the operand as the second 8 bits.

- (i) What is the maximum number of memory locations which can be directly addressed? [1]

- (ii)

| Consider the instruction:            |   |   |   |   |   |   |   |   |   |   |   |  |

|--------------------------------------|---|---|---|---|---|---|---|---|---|---|---|--|

| 0                                    | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |  |

| Describe what this instruction does. |   |   |   |   |   |   |   |   |   |   |   |  |

- (iii) Programmers prefer to write machine code instructions in hexadecimal. Explain why. [1]

- (iv) What is the hexadecimal number for the machine code instruction shown in part (b)(ii)? [1]

- (v) Show the 16-bit machine code for the following instruction: JPE 204

[2]

zak@zakonweb.com

0

0

0

1

www.zakonweb.com

[2]

## Topic: 1.4.4 Assembly Language

(b) Use the ASCII code table to trace execution of the given program.

| ASCII code table (part) |         |           |         |           |         |  |  |

|-------------------------|---------|-----------|---------|-----------|---------|--|--|

| Character               | Decimal | Character | Decimal | Character | Decimal |  |  |

| <space></space>         | 32      | l I       | 73      | R         | 82      |  |  |

| Α                       | 65      | J         | 74      | S         | 83      |  |  |

| В                       | 66      | к         | 75      | Т         | 84      |  |  |

| С                       | 67      | L         | 76      | U         | 85      |  |  |

| D                       | 68      | М         | 77      | V         | 86      |  |  |

| E                       | 69      | N         | 78      | W         | 87      |  |  |

| F                       | 70      | 0         | 79      | Х         | 88      |  |  |

| G                       | 71      | Р         | 80      | Y         | 89      |  |  |

| н                       | 72      | Q         | 81      | Z         | 90      |  |  |

| ACC | Location<br>450 | OUTPUT |

|-----|-----------------|--------|

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

|     |                 |        |

| 300                             | LDI   | 450                          |

|---------------------------------|-------|------------------------------|

| 301                             | CMP   | 32                           |

| 302                             | JPE   | 308                          |

| 303                             | OUTCH |                              |

| 304                             | LDD   | 450                          |

| 305                             | INC   | ACC                          |

| 306                             | STO   | 450                          |

| 307                             | JMP   | 300                          |

| 308                             | END   |                              |

| 450                             | 7     | ر ر<br><sup>500</sup><br>ر ر |

| 500<br>501<br>502<br>503<br>504 |       | 65<br>74<br>65<br>90<br>32   |